## MN54L-P15

## **Bluetooth® Low Energy Module**

**Datasheet** Version A

**Ordering Code**

MN54L-P15 module for Box packaging: MN-L15Q1-01A-PB

## **BLE Solution: Nordic NRF54L15**

| RF IC              | Crystal                        | PCB antenna |

|--------------------|--------------------------------|-------------|

| Nordic NRF54L15/V1 | 32MHz/20ppm/CL=8PF<br>Embedded | Embedded    |

i

## **Overview and Benefits**

#### **Overview**

The MN54L-P15 from **Aradconn** is a highly flexible, ultra-low power, Bluetooth Low Energy module based on the nRF54L15 SoC from Nordic Semiconductor. With an Arm® Cortex®-M33 with FPU 32-bit processor, embedded 2.4GHz transceiver, and integrated PCB antenna. Providing full use of the nRF54L15's capabilities and peripherals, which include I2C, SPI,QSPI, UART, I2S, ADC, GPIO, PWM, and NFC interfaces.

### **Benefits**

- Bluetooth qualification and Regulatory certification reduce the burden to enter the market.

- Complete RF solution with no additional RF design, allowing faster time to launch a new product, and providing long working distance.

MN54L-P: up to 500 meters in open space. @1 Mbps

- Compact size: (L) 14.5 x (W) 9.3 x (H) 2.1mm.

- Provides flexibility in the OEM's application development choice with full support for using Nordic SDK and firmware tools.

## Contents

| 1. Features                                          | 1  |

|------------------------------------------------------|----|

| 1.1 Features                                         | 1  |

| 2. Mechanical specifications                         | 3  |

| 2.1 Dimensions                                       | 3  |

| 2.2 Footprint                                        | 4  |

| 2.3 Module Marking                                   | 5  |

| 3. Pin Assignment                                    | 6  |

| 3.1 GPIO Recommended usage                           | 10 |

| 4 Layout design notes                                | 12 |

| 4.1 Recommended RF layout and ground plane           | 12 |

| 4.2 Not Recommended RF layout and ground plane       | 13 |

| 4.3 Antenna keep out when proximity to Metal         | 13 |

| 5. Electrical Specification                          | 14 |

| 5.1 Absolute Maximum Ratings                         | 14 |

| 5.2 Operation Conditions                             | 14 |

| 5.3 Radio Specifications                             | 15 |

| 5.4 Antenna information                              | 16 |

| 5.4.1 The orientation of Antenna                     | 16 |

| 5.4.2 Antenna Gain and Efficiency                    | 16 |

| 5.4.3 Antenna Pattern 2D                             | 17 |

| 5.5 CPU Specifications                               | 18 |

| 5.6 Power Management                                 | 18 |

| 5.7 System Clock                                     | 19 |

| 5.8 Block Diagram                                    | 20 |

| 6. BN54L-P15 evaluation board                        | 21 |

| 6.1 BN54L-P15 component placement                    | 21 |

| 6.2 BN54L-P15 schematic                              | 22 |

| 7. Product Information                               | 23 |

| 7.1 Mass production information                      | 23 |

| 7.2 Packing information                              | 24 |

| 7.3 Ordering Code                                    | 25 |

| 8. Bluetooth qualification& Regulatory certification | 26 |

| 8.1 Bluetooth qualification                          | 26 |

| 8.2 USA (FCC Certificate)                            | 26 |

| 8.3 Canada (IC Certificate)                          | 27 |

| 8.4 European Union (CE)           | 29 |

|-----------------------------------|----|

| 8.5 Australia / New Zealand (RCM) |    |

| 8.6 NCC Certificate (Taiwan)      |    |

| 9. RoHS & REACH Report            |    |

| 10. Life support warning          |    |

| Revision history                  | 31 |

#### 1. Features

#### 1.1 Features

#### • 2.4 GHz transceiver

- -96 dBm sensitivity in 1Mbps Bluetooth® low energy mode

- -104 dBm sensitivity in 125kbps Bluetooth® low energy mode(long range)

- -8 to +8dBm TX power, configurable in 1 dB steps

- Supported data rates:

- Bluetooth® 5 − 2 Mbps, 1 Mbps, 500 kbps, and 125 kbp

- IEEE 802.15.4-2020 250 kbps

- Proprietary 2.4 GHz –4Mbps, 2 Mbps, 1 Mbps

- 9.1 mA/ @3V DC/DC peak current in TX (7 dBm)

- 2.1 mA/@3V DC/DC peak current in RX

- RSSI (1 dB resolution)

#### Arm® Cortex®-M33 32-bit processor with TrustZone® technology, 128 MHz

- 500 EEMBC CoreMark® score running from non-volatile memory

- Single-precision floating-point unit (FPU)

- Memory protection unit (MPU)

- Digital signal processing (DSP) instructions

- Serial wire debug (SWD)

#### Operating condition

- 1.7 V to 3.6 V supply and I/O voltage

- Single 32 MHz crystal operation

- Optional 32.768 kHz clock

- Operating temperature from -40°C to 85°C

#### Memory

• 1.524MB NVM/256 kB RAM

#### Peripherals

- RISC-V 128MHZ Coprocessor

- 31 general purpose I/O pins

- Global RTC (GRTC) that can run in System OFF mode and implement a shared system timer

- Seven 32-bit timers with counter mode

- Up to five fully featured serial interfaces with EasyDMA, supporting I2C, SPI controller/peripheral, and UART

- One high-speed SPIM up to 32 MHz, four up to 8 MHz

- I2C up to 400 kHz

- Three pulse width modulator (PWM) units with EasyDMA

- I2S two channel Inter-IC sound interface

- ADC with up to eight programmable gain channels.

14-bit at 31.25ksps, 12-bit at 250 ksps, and up to 10-bit at 2 Msps.

- Pulse density modulation (PDM) interface

- Near field communication (NFC)

- Up to two quadrature decoders (QDEC)

- Comparator and low-power comparator with wake-up from System OFF mode

- Temperature sensor

## 2. Mechanical specifications

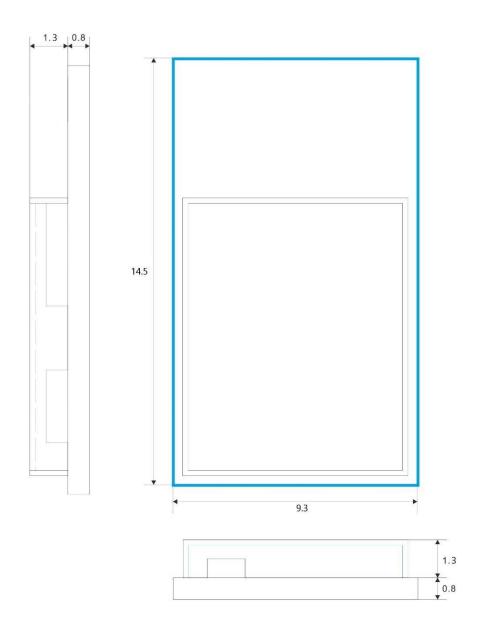

## 2.1 Dimensions

All dimensions are in millimeters.

| Item   | Dimension | Tolerance |

|--------|-----------|-----------|

| Length | 14.5mm    | ±0.30 mm  |

| Width  | 9.3mm     | ±0.30mm   |

| Height | 2.1mm     | ±0.30mm   |

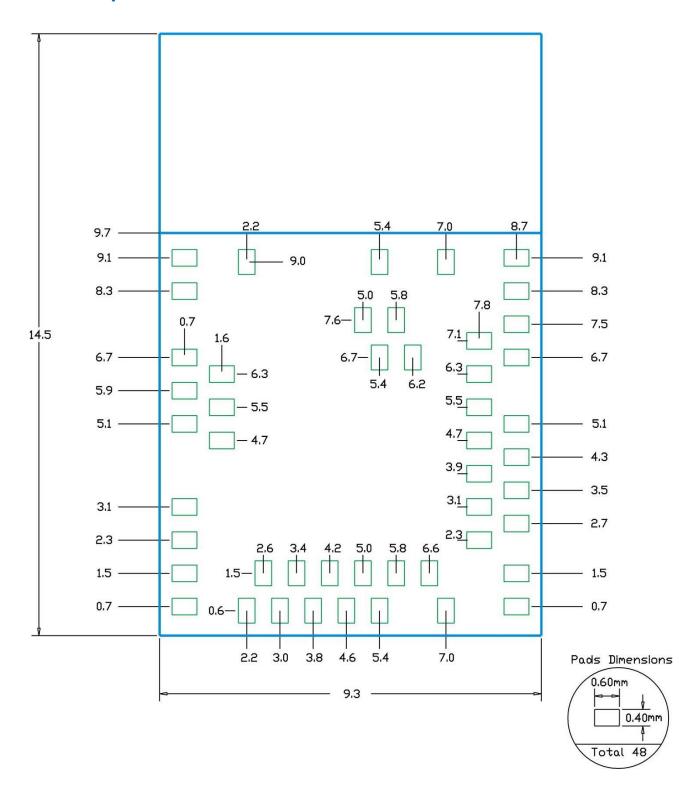

## 2.2 Footprint

All dimensions are in millimeters.

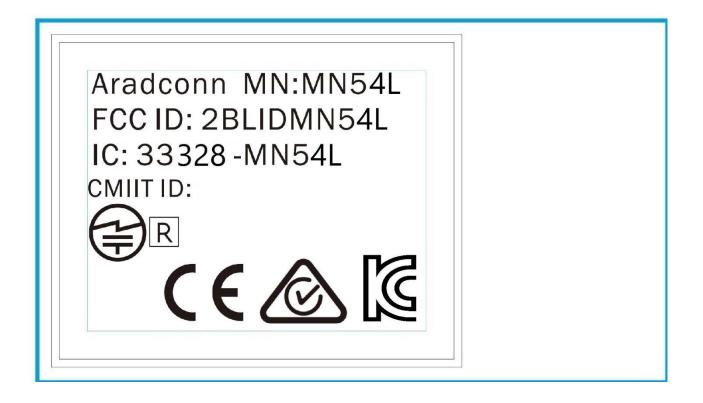

## 2.3 Module Marking

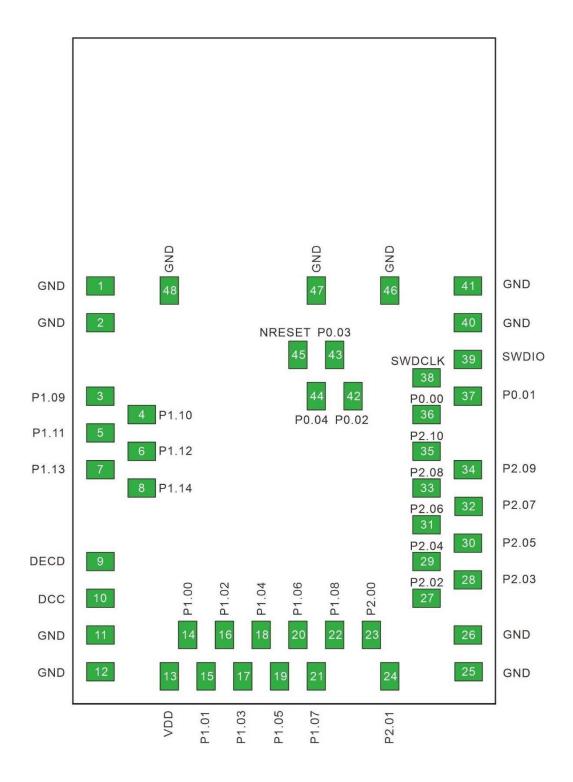

## 3. Pin Assignment

| Pin No.      | Name    | Pin function | Description                                       |

|--------------|---------|--------------|---------------------------------------------------|

| (1)          | GND     | Ground       | The pad must be connected to a solid ground plane |

| (2)          | GND     | Ground       | The pad must be connected to a solid ground plane |

| (3)          | P1.09   | Digital I/O  | General-purpose I/O                               |

|              | Radio 0 | Digital I/O  | DFEGPIO : Direction Finding Antenna select GPIO   |

| (4)          | P1.10   | Digital I/O  | General-purpose I/O                               |

|              | Radio 1 | Digital I/O  | DFEGPIO: Direction Finding Antenna select GPIO    |

| (5)          | P1.11   | Digital I/O  | General-purpose I/O                               |

| _            | Radio 2 | Digital I/O  | DFEGPIO : Direction Finding Antenna select GPIO   |

| _            | AIN4    | Analog input | Analog input                                      |

|              |         | Clock pin    | Can be set as TWI                                 |

| (6)          | P1.12   | Digital I/O  | General-purpose I/O                               |

|              | Radio 3 | Digital I/O  | DFEGPIO : Direction Finding Antenna select GPIO   |

|              | AIN5    | Analog input | Analog input                                      |

|              |         | Clock PIN    | Can be set as TWI                                 |

| (7)          | P1.13   | Digital I/O  | General-purpose I/O                               |

| _            | Radio 4 | Digital I/O  | DFEGPIO : Direction Finding Antenna select GPIO   |

|              | AIN6    | Analog input | Analog input                                      |

| (8)          | P1.14   | Digital I/O  | General-purpose I/O                               |

| _            | Radio 5 | Digital I/O  | DFEGPIO: Direction Finding Antenna select GPIO    |

|              | AIN7    | Analog input | Analog input                                      |

| (9)          | DECD    | Power        | 0.9 V regulator supply decoupling                 |

| (10)         | DCC     | Power        | DC/DC regulator output                            |

| (11)         | GND     | Ground       | The pad must be connected to a solid ground plane |

| (12)         | GND     | Ground       | The pad must be connected to a solid ground plane |

| (13)         | VDD     | Power        | Power supply                                      |

| (14)         | P1.00   | Digital I/O  | General-purpose I/O                               |

|              | XL1     | Analog input | Connection to 32.768kHz crystal (LFXO)            |

| (15)         | P1.01   | Digital I/O  | General-purpose I/O                               |

|              | XL2     | Analog input | Connection to 32.768kHz crystal (LFXO)            |

| (16)         | P1.02   | Digital I/O  | General-purpose I/O                               |

|              | NFC1    | NFC input    | NFC antenna connection                            |

| (17)         | P1.03   | Digital I/O  | General-purpose I/O                               |

| _            | NFC2    | NFC input    | NFC antenna connection                            |

|              |         | Clock pin    | Can be set as TWI when NFC is unused              |

| (18)         | P1.04   | Digital I/O  | General-purpose I/O                               |

|              | AIN0    | Analog input | Analog input                                      |

|              |         | Clock PIN    | Can be set as TWI when NFC is unused              |

| (19)         | P1.05   | Digital I/O  | General-purpose I/O                               |

| ·            | Radio 6 | Digital I/O  | DFEGPIO : Direction Finding Antenna select GPIO   |

|              | AIN1    | Analog input | Analog input                                      |

| (20)         | P1.06   | Digital I/O  | General-purpose I/O                               |

|              | AIN2    | Analog input | Analog input                                      |

| (21)         | P1.07   | Digital I/O  | General-purpose I/O                               |

| <del>_</del> | AIN3    | Analog input | Analog input                                      |

| Pin No. | Name     | Pin function            | Description                                       |

|---------|----------|-------------------------|---------------------------------------------------|

| (22)    | P1.08    | Digital I/O             | General-purpose I/O                               |

| , ,     | CLK16M   | Clock PIN               | GRTC HF clock output                              |

|         | EXTREF   | Analog input            | External reference for SAADC                      |

|         |          |                         |                                                   |

| (23)    | P2.00    | Digital I/O             | General-purpose I/O                               |

|         |          | Digital I/O             | SPIM DCX                                          |

|         |          | Digital I/O             | UARTE RXD                                         |

|         |          | Digital I/O             | QSPI D3                                           |

| (24)    | P2.01    | Digital I/O             | General-purpose I/O                               |

|         |          | Clock PIN               | SPIM SCK                                          |

|         |          | Clock PIN               | SPIS SCK                                          |

|         |          | Clock PIN               | QSPI SCK                                          |

| (25)    | GND      | Ground                  | The pad must be connected to a solid ground plane |

| (26)    | GND      | Ground                  | The pad must be connected to a solid ground plane |

| (27)    | P2.02    | Digital I/O             | General-purpose I/O                               |

|         |          | Digital I/O             | SPIM SDO                                          |

|         |          | Digital I/O             | SPIS SDO                                          |

|         |          | Digital I/O             | UARTE TXD                                         |

|         |          | Digital I/O             | QSPI DO                                           |

| (28)    | P2.03    | Digital I/O             | General-purpose I/O                               |

|         |          | Digital I/O             | QSPI D2                                           |

| (29)    | P2.04    | Digital I/O             | General-purpose I/O                               |

|         |          | Digital I/O             | SPIM SDI                                          |

|         |          | Digital I/O             | SPIS SDI                                          |

|         |          | Digital I/O             | UARTE CTS                                         |

| (20)    | D2 0F    | Digital I/O             | QSPI D1                                           |

| (30)    | P2.05    | Digital I/O             | General-purpose I/O                               |

|         |          | Digital I/O             | SPIM CS                                           |

|         |          | Digital I/O Digital I/O | UARTE RTS  QSPI CS                                |

| (31)    | P2.06    | Digital I/O             | General-purpose I/O                               |

| (31)    | F 2.00   | Clock PIN               | SPIM SCK                                          |

|         |          | Clock PIN               | SPIS SCK                                          |

| (32)    | P2.07    | Digital I/O             | General-purpose I/O                               |

| (32)    | 1 2.07   | Digital I/O             | SPIM DCX                                          |

|         | <u>-</u> | Digital I/O             | UART RXD                                          |

| (33)    | P2.08    | Digital I/O             | General-purpose I/O                               |

| (00)    |          | Digital I/O             | SPIM SDO                                          |

|         |          | Digital I/O             | SPIS SDO                                          |

|         |          | Digital I/O             | UARTE TXD                                         |

| (34)    | P2.09    | Digital I/O             | General-purpose I/O                               |

| V- 1    |          | Digital I/O             | SPIM SDI                                          |

|         |          | Digital I/O             | SPIS SDI                                          |

|         |          | Digital I/O             | UART CTS                                          |

|         |          |                         |                                                   |

|         |          |                         |                                                   |

| Pin No. | Name         | Pin function | Description                                         |

|---------|--------------|--------------|-----------------------------------------------------|

| (35)    | P2.10        | Digital I/O  | General-purpose I/O                                 |

|         |              | Digital I/O  | SPIM CS                                             |

|         |              | Digital I/O  | UARTE RTS                                           |

| (36)    | P0.00        | Digital I/O  | General-purpose I/O                                 |

| (37)    | P0.01        | Digital I/O  | General-purpose I/O                                 |

| (38)    | SWDCLK       | Debug        | Serial wire clock. Input with onchip pull-up.       |

| (39)    | SWDIO        | Debug        | Serial wire data. Bidirectional with standard-drive |

|         |              |              | and on-chip pull-down.                              |

| (40)    | GND          | Ground       | The pad must be connected to a solid ground plane   |

| (41)    | GND          | Ground       | The pad must be connected to a solid ground plane   |

| (42)    | P0.02        | Digital I/O  | General-purpose I/O                                 |

| (43)    | P0.03        | Digital I/O  | General-purpose I/O                                 |

|         | GRTCPWM      | Clock PIN    | GRTC PWM output                                     |

| (44)    | P0.04        | Digital I/O  | General-purpose I/O                                 |

|         | GRTCLFCLKOUT | Clock PIN    | GRTC LF clock output                                |

| (45)    | nRESET       | Reset        | Pin reset with on-chip pull-up                      |

| (46)    | GND          | Ground       | The pad must be connected to a solid ground plane   |

| (47)    | GND          | Ground       | The pad must be connected to a solid ground plane   |

| (48)    | GND          | Ground       | The pad must be connected to a solid ground plane   |

## **3.1 GPIO Recommended usage**

| Module  | NRF54L15  | Recommended usage                                  |  |  |

|---------|-----------|----------------------------------------------------|--|--|

| PIN NO. | GPIO      |                                                    |  |  |

|         | QSPI      |                                                    |  |  |

| 23      | P2.00     | QSPI D3                                            |  |  |

| 24      | P2.01     | QSPI SCK                                           |  |  |

| 27      | P2.02     | QSPI D0                                            |  |  |

| 28      | P2.03     | QSPI D2                                            |  |  |

| 29      | P2.04     | QSPI D1                                            |  |  |

| 30      | P2.05     | QSPI CS                                            |  |  |

| TWI (N  | ote: TWIM | and TWIS must use clock pins for both SDA and SCL) |  |  |

| 5       | P1.11     | TWI                                                |  |  |

| 6       | P1.12     | TWI                                                |  |  |

| 17      | P1.03     | Can be set as TWI when NFC is unused               |  |  |

| 18      | P1.04     | Can be set as TWI when NFC is unused               |  |  |

| 43      | P0.03     | Can be set as TWI when PWM output is unused        |  |  |

| 44      | P0.04     | Can be set as TWI when LF Clock output is unused   |  |  |

|         |           | UARTE 00/20                                        |  |  |

| 23      | P2.00     | RXD                                                |  |  |

| 27      | P2.02     | TXD                                                |  |  |

| 29      | P2.04     | CTS                                                |  |  |

| 30      | P2.05     | RTS                                                |  |  |

|         |           | UARTE 00/21                                        |  |  |

| 32      | P2.07     | RXD                                                |  |  |

| 33      | P2.08     | TXD                                                |  |  |

| 34      | P2.09     | CTS                                                |  |  |

| 35      | P2.10     | RTS                                                |  |  |

|         |           | SPI 00/20                                          |  |  |

| 23      | P2.00     | SPIM DCX                                           |  |  |

| 24      | P2.01     | SPIM/SPIS SCK                                      |  |  |

| 27      | P2.02     | SPIM/SPIS SDO                                      |  |  |

| 29      | P2.04     | SPIM/SPIS SDI                                      |  |  |

| 30      | P2.05     | SPIM CS                                            |  |  |

|         |           | SPI 00/21                                          |  |  |

| 31      | P2.06     | SPIM/SPIS SCK                                      |  |  |

| 32      | P2.07     | SPIM DCX                                           |  |  |

| 33      | P2.08     | SPIM/SPIS SDO                                      |  |  |

| 34      | P2.09     | SPIM/SPIS SDI                                      |  |  |

| 35      | P2.10     | SPIM CS                                            |  |  |

|    | NFC   |                                         |  |  |

|----|-------|-----------------------------------------|--|--|

| 17 | P1.02 | NFC1                                    |  |  |

| 18 | P1.03 | NFC2                                    |  |  |

|    |       | PWM                                     |  |  |

| 43 | P0.03 | PWM                                     |  |  |

|    |       | Clock Output                            |  |  |

| 22 | P1.08 | GRTC HF clock output(16MHZ)             |  |  |

| 44 | P0.04 | GRTC LF clock output (32.768KHZ)        |  |  |

|    |       | Analog Input                            |  |  |

| 19 | P1.05 | AIN1                                    |  |  |

| 20 | P1.06 | AIN2                                    |  |  |

| 21 | P1.07 | AIN3                                    |  |  |

| 22 | P1.08 | External reference for SAADC            |  |  |

| 5  | P1.11 | AIN4                                    |  |  |

| 6  | P1.12 | AIN5                                    |  |  |

| 7  | P1.13 | AIN6                                    |  |  |

| 8  | P1.14 | AIN7                                    |  |  |

|    | Radio | (Direction Finding Antenna select GPIO) |  |  |

| 3  | P1.09 | Radio 0                                 |  |  |

| 4  | P1.10 | Radio 1                                 |  |  |

| 5  | P1.11 | Radio 2                                 |  |  |

| 6  | P1.12 | Radio 3                                 |  |  |

| 7  | P1.13 | Radio 4                                 |  |  |

| 8  | P1.14 | Radio 5                                 |  |  |

## 4 Layout design notes

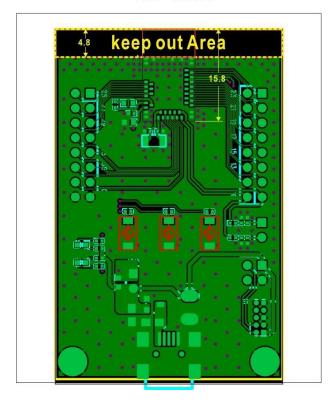

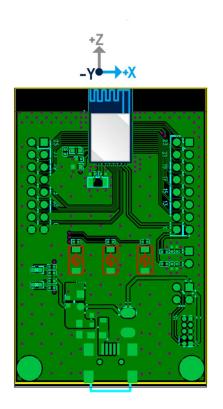

## 4.1 Recommended RF layout and ground plane

It is recommended to place the module:

- In the center (horizontal) of any mother PCB edge, with GND planes to the left and right

- Keep out Area should be included in the corresponding position of the antenna in each layer.

- Add via hole around GND pads on the mother PCB as many as you can, especially on the four corners and antenna area.

#### **Bottom VIEW**

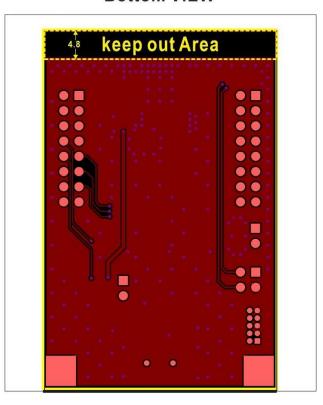

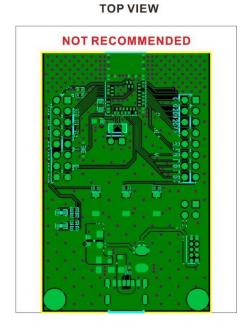

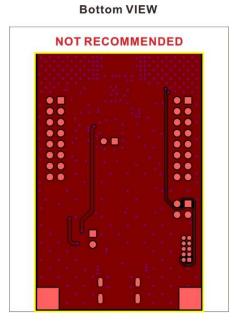

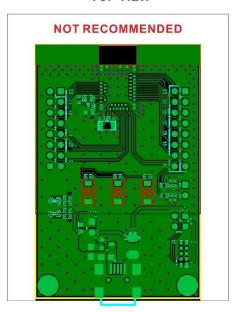

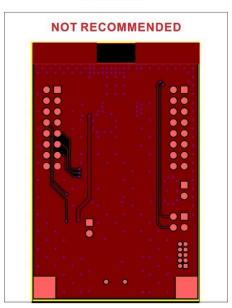

### 4.2 Not Recommended RF layout and ground plane

**TOP VIEW**

**Bottom VIEW**

## 4.3 Antenna keep out when proximity to Metal

- The minimum safe distance for metals without seriously compromising the antenna tuning is 4cm (bottom, top, left, right).

- Metal close to the antenna (bottom, top, left, right) will degrade RF performance. Any metal closer than 2 cm will significantly degrade RF performance.

# 5. Electrical Specification5.1 Absolute Maximum Ratings

Maximum ratings are the extreme limits to which the chip can be exposed for a limited amount of time without causing permanent damage. Prolonged exposure to absolute maximum ratings may affect the device's reliability.

| Parameter                    | Min.   | Max.             | Unit               |

|------------------------------|--------|------------------|--------------------|

| Supply voltage               |        |                  |                    |

| VDD                          | -0.3   | +3.6             | V                  |

| VSS                          |        | 0                | V                  |

| I/O pin voltage              |        |                  |                    |

| Vı/o, VDD ≤3.5 V             | -0.3   | VDD+0.3          | V                  |

| VI/O, VDD >3.5 V             |        | 3.6              | V                  |

| Environmental                |        |                  |                    |

| Storage temperature          | -40    | +105             | °C                 |

| MSL (moisture sensitivity le | vel)   | 2                |                    |

| ESD HBM (human body mo       | odel)  | 1                | KV                 |

| ESD CDM (charged device      | model) | 500              | V                  |

| Flash memory                 |        |                  |                    |

| Endurance                    |        | 10000            | Write/erase cycles |

| Retention                    |        | 10 years at 85°C |                    |

## **5.2 Operation Conditions**

| Parameter                 | Min. | Nom. | Max. | Units |

|---------------------------|------|------|------|-------|

| VDD (independent of DCDC) | 1.7  |      | 3.5  | V     |

| VDD during power on reset | 1.75 |      |      | V     |

| Operating temperature     | -40  | 25   | 85   | °C    |

## **5.3 Radio Specifications**

| Parameter              | Description                                                | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------------------------|------|------|------|------|

| Operating frequencies  | BLE                                                        | 2402 |      | 2480 | MHz  |

| Channel spacing        | BLE                                                        |      | 2    |      | MHz  |

| Frequency deviation    | BLE 1Mbps                                                  |      | ±250 |      | kHz  |

|                        | BLE 2Mbps                                                  |      | ±500 |      | kHz  |

| On-the-air data rate   |                                                            | 125  |      | 4000 | kHz  |

|                        | Transmitter                                                |      |      |      |      |

| TX power               | Setting at +7dBm                                           |      | +7   |      | dBm  |

| RF power control range | -8 ~+8dBm, in 1db step                                     | -16  |      | +7   | dBm  |

| TX current (TX only)   | DCDC@3V/+7 dBm                                             |      | 9.1  |      | mA   |

|                        | Receiver                                                   |      |      |      |      |

| Receive Sensitivity    | 1Msps BLE ideal transmitter                                |      | -96  |      | dBm  |

|                        | Packet <=37bytes BRE=0.1%                                  |      |      |      |      |

|                        | 2Msps BLE ideal transmitter Packet <=37bytes BRE=0.1%      |      | -94  |      | dBm  |

|                        | 125ksps BLE ideal transmitter<br>Packet <=37bytes BRE=0.1% |      | -104 |      | dBm  |

| RX current (RX only)   | DCDC@3V/1Msps BLE                                          |      | 2.1  |      | mA   |

|                        | DCDC@3V/2Msps BLE                                          |      | 2.2  |      | mA   |

| RSSI                   | RSSI Accuracy Valid range                                  | -90  |      | -30  | dBm  |

|                        | RSSI resolution                                            |      | 1    |      | dB   |

|                        | Sample period                                              |      | 0.25 |      | us   |

| Antenna gain           |                                                            |      | 0.8  |      | dBi  |

## **5.4** Antenna information

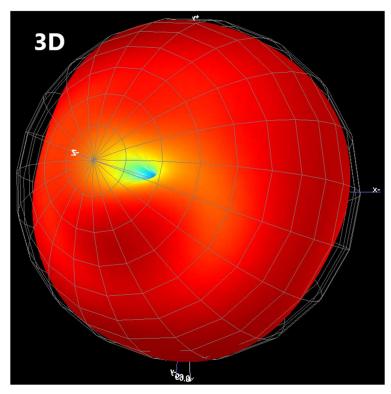

The antenna test report is based on the BN54L-P15 with a ground plane size of 60 mm x 40 mm.

## **5.4.1** The orientation of Antenna

## **5.4.2** Antenna Gain and Efficiency

| Frequency | Gain(dBi) | Efficiency |

|-----------|-----------|------------|

| 2400MHZ   | 0.08      | 40         |

| 2410MHZ   | 0.47      | 41         |

| 2420MHZ   | 0.72      | 42         |

| 2430MHZ   | 0.80      | 45         |

| 2440MHZ   | 0.79      | 46         |

| 2450MHZ   | 0.69      | 45         |

| 2460MHZ   | 0.54      | 43         |

| 2470MHZ   | 0.43      | 42         |

| 2480MHZ   | 0.18      | 40         |

| 2490MHZ   | -0.15     | 36         |

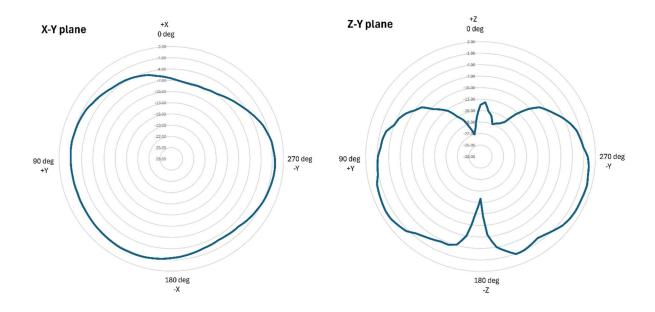

## 5.4.3 Antenna Pattern 2D

## **5.5 CPU Specifications**

The ARM® Cortex®-M33 processor with floating-point unit (FPU) has a 32-bit instruction set.

## 128 MHz RISC-V coprocessor : VPR RISC-V is a small, efficient CPU developed by Nordic Semiconductor.

| Memory        | NVM                                              | RAM   |      |      |                  |

|---------------|--------------------------------------------------|-------|------|------|------------------|

|               | 1522KB                                           | 256KB |      |      |                  |

| Parameter     | Description                                      | Min.  | Тур. | Max. | Unit             |

| CoreMark      | running from flash, cache enabled                |       | 500  |      | CoreMark         |

| CoreMark /MHz | running from flash, cache enabled                |       | 3.9  |      | CoreMark/<br>MHz |

| CPU current   | Running Coremark@128MHz from NVM, cache enabled  |       | 2.6  |      | mA               |

| 3. 3 ca./ciic | running Coremark@128MHz from RAM, cache disabled |       | 2.9  |      | mA               |

## **5.6 Power Management**

| Parameter  | Description                                  | Min. | Тур. | Max. | Unit |

|------------|----------------------------------------------|------|------|------|------|

|            | No RAM retention, Wake on pin                |      | 0.6  |      | uA   |

| System OFF | No RAM retention, Wake on pin +GRTC ,LFXO    |      | 0.8  |      | uA   |

|            | No RAM retention, Wake on pin                |      | 0.7  |      | uA   |

| System ON  | n ON Full RAM retention, Wake on pin         |      | 3.0  |      | uA   |

|            | Full RAM retention, Wake on pin + GRTC ,LFXO |      | 3.1  |      | uA   |

|            | Full RAM retention, Wake on pin + GRTC ,LFRC |      | 3.7  |      | uA   |

### **5.7 System Clock**

The MN54L series requires two clocks, a high frequency clock and a low frequency clock.

The high frequency clock (HFCLK)

HFCLK is provided on-module by a high-accuracy 32 MHz/±20 ppm/CL=8PF crystal for radio and CPU operation.

The low frequency clock (LFCLK)

LFCLK can be provided internally by an RC oscillator (±250 ppm) with calibration, or externally by a 32.768 kHz crystal.

#### Internal 32.768 kHz RC oscillator (LFRC)

| Description                                                                                     | Min. | Тур.             | Max. | Unit |

|-------------------------------------------------------------------------------------------------|------|------------------|------|------|

| Nominal frequency                                                                               |      | 32.768           |      | kHz  |

| Frequency tolerance for LFRC after calibration (calibration performed at least every 8 seconds) |      |                  | ±500 | ppm  |

| Run current for 32.768 kHz RC oscillator                                                        |      | <mark>0.7</mark> |      | uA   |

| Startup time for 32.768 kHz RC oscillator                                                       |      | 1000             |      | us   |

#### External 32.768 kHz crystal oscillator (LFXO)

| Parameter | Description                                   | Min. | Тур.   | Max. | Unit |

|-----------|-----------------------------------------------|------|--------|------|------|

|           | Crystal frequency                             |      | 32.768 |      | kHz  |

|           | Frequency tolerance requirement for BLE stack |      |        | ±500 | ppm  |

|           | Frequency tolerance requirement for ANT stack |      |        | ±50  | ppm  |

|           | Run current for 32.768 kHz crystal oscillator |      | 0.23   |      | uA   |

| CL        | Load capacitance                              | 6    |        | 9    | pF   |

An external crystal provides the lowest power consumption and greatest accuracy.

Using the internal RC oscillator with calibration provides acceptable performance for BLE stack at a reduced cost and slight increase in power consumption.

#### Important:

- The ANT protocol requires the use of an external crystal for high accuracy.

- Nordic SDK example program P1.00/P1.01 as external LFXO, you need an external crystal to work.

- Nordic SDK example program P1.00/P1.01 as external LFXO, if you would like to reduce material

cost, save layout space or requires 2 more GPIO for application. you need program P1.00/P1.01

as internal LFRC.

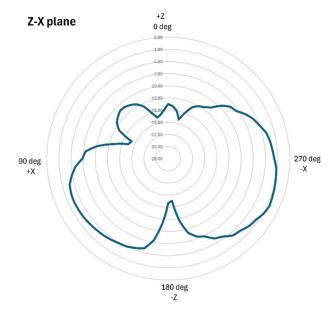

## 5.8 Block Diagram

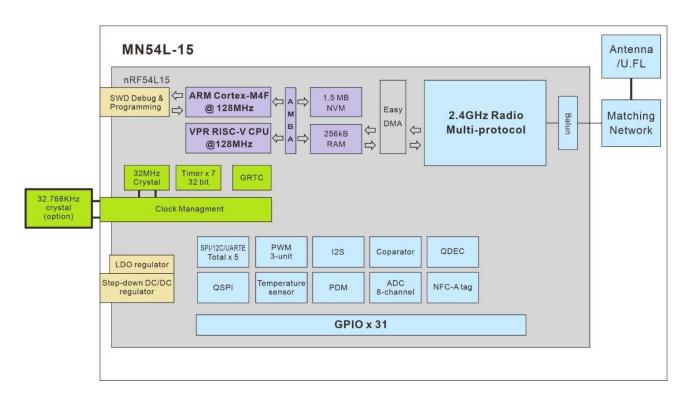

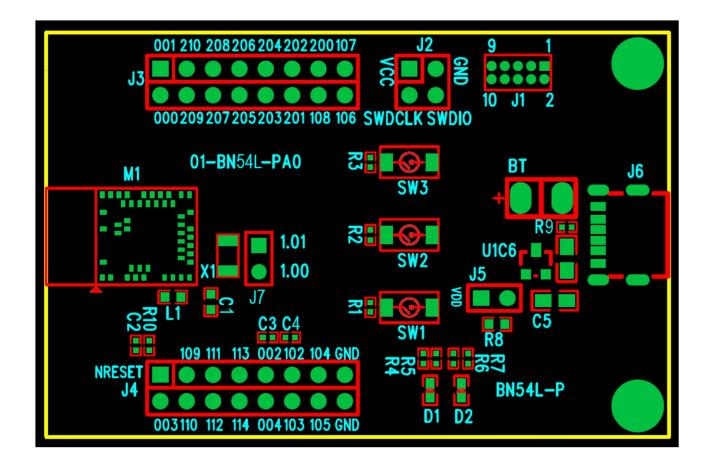

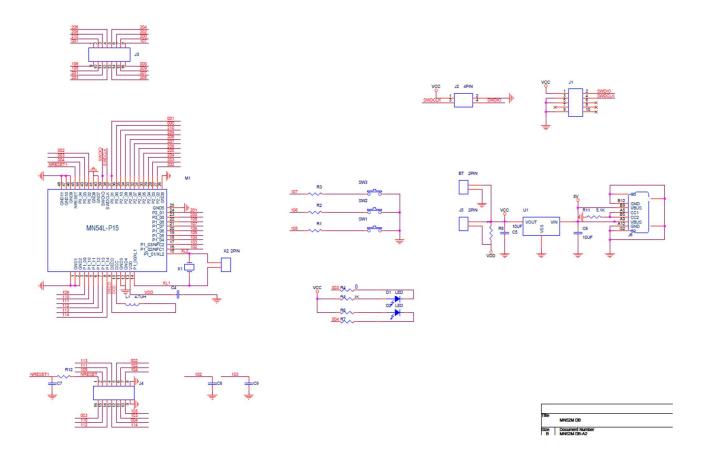

# 6. BN54L-P15 evaluation board 6.1 BN54L-P15 component placement

#### BN54L-P15 is a full-featured evaluation board for MN54L-P15 that supports:

M1:MN54L-P15 module

J6: A power over Type C USB

J3/J4: Complete I/O pinout to headers

J1/J2: On-board programming and debugging interface

X1:32.768 kHz crystal

D1: One user LED

SW1/SW2/SW3: Three user buttons

## 6.2 BN54L-P15 schematic

#### **REMARK:**

When using internal 32.768kHz RC oscillator, please remove X1 and calibration performed at least every 8 seconds.

## 7. Product Information

## **7.1 Mass production information**

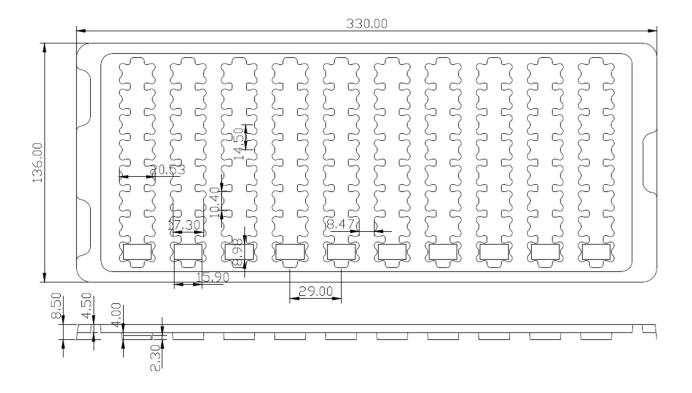

#### 7.1.1 Tray Packaging:

Material: anti-static PET PET thickness: 0.8mm

Dimension: 322mm x 136mm x 8.5mm

The tray is designed for direct use on a SMT automatic machine.

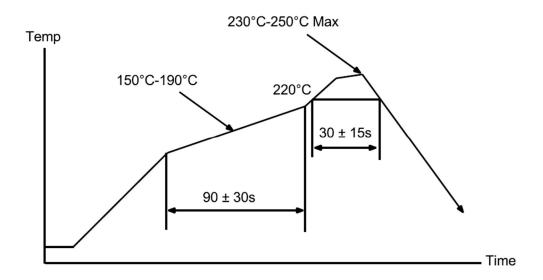

#### **7.1.2** Reflow Parameters

## **7.2 Packing information**

| Туре   | Quantity           | Dimension<br>(L)x(W)x(H) | Gross Weight |

|--------|--------------------|--------------------------|--------------|

| Tray   | 80 pcs per tray    | 322x136x8.5mm            |              |

| Carton | 1040 pcs(13 trays) | 36x20x12cm               | 3.0Kg        |

## **7.3 Ordering Code**

| Model     | Ordering code   | Photo |

|-----------|-----------------|-------|

|           |                 |       |

| MN54L-P15 | MN-L15Q1-01A-PB |       |

Ordering code: MN-L15Q1-01A-PB

MN: Module/Nordic

L15Q1: NRF54L15/QFN/V1

01A: Aradconn standard module without customer code

PB: PCB antenna/Box packing

#### **MN54L Series**

| Model     | IC/Version  | Antenna           | Ordering code   | Quantity |

|-----------|-------------|-------------------|-----------------|----------|

| MN54L-C15 | NRF54L15/V1 |                   | MN-L15Q1-01A-CB | 1040     |

| MN54L-C10 | NRF54L10/V1 | Chip              | MN-L10Q1-01A-CB | 1040     |

| MN54L-C05 | NRF54L05/V1 | -                 | MN-L05Q1-01A-CB | 1040     |

|           |             |                   |                 |          |

| MN54L-P15 | NRF54L15/V1 |                   | MN-L15Q1-01A-PB | 1040     |

| MN54L-P10 | NRF54L10/V1 | РСВ               | MN-L10Q1-01A-PB | 1040     |

| MN54L-P05 | NRF54L05/V1 | _                 | MN-L05Q1-01A-PB | 1040     |

|           |             |                   |                 |          |

| MN54L-U15 | NRF54L15/V1 | U.FL<br>Connector | MN-L15Q1-01A-UB | 1040     |

# 8. Bluetooth qualification Regulatory certification 8.1 Bluetooth qualification

The MN54L-P15 Bluetooth Low Energy module is based on Nordic Semiconductor's NRF54 series SOC and listed on the Bluetooth SIG website as a qualified End Product.

| Model | Bluetooth Version | DID | QDID     | Company             |

|-------|-------------------|-----|----------|---------------------|

| MN54L | 6.0               |     | (Nordic) | — Arad Connectivity |

|       |                   |     | (Nordic) |                     |

### 8.2 USA (FCC Certificate)

#### **8.2.1 FCC ID and Labeling requirements**

The MN54L series hold full modular certification, are assigned the

FCC ID number: 2BLIDMN54L

If the FCC ID is not visible when the module is installed inside OEM device, then the outside of the finished product must also display a label referring to the enclosed module. The end product must in any case be labelled on the exterior with:

Contains FCC ID: 2BLIDMN54L

#### 8.2.2 FCC Notice:

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

**8.2.3 CAUTION:**

The OEM should have their device which incorporates the MN54L series tested by

a qualified test Lab to verify compliance with FCC Part 15 Subpart B limits for

unintentional radiators.

**8.2.4 RF Exposure Statement:**

This module is approved for installation into mobile and/or portable host

platforms.

This device is intended only for OEM integrators under the following conditions:

(1) The transmitter module may not be co-located with any other transmitter or

antenna.

(If the condition above is met, further transmitter test will not be required.)

(2) The OEM integrator is still responsible for testing their end-product for any

additional compliance requirements required for satisfying RF Exposure

compliance when this module installed.

8.3 Canada (IC Certificate)

8.3.1 IC ID and Labeling requirements

The MN54L series hold full modular certification, are assigned the

IC ID number: 33328-MN54L

If the IC ID is not visible when the module is installed inside OEM device, then the outside of the finished product must also display a label referring to the enclosed

module. The end product must in any case be labelled on the exterior with:

Contains IC ID: 33328-MN54L

27

#### **8.3.2 IC Notice:**

This device complies with Industry Canada license-exempt RSSs. Operation is subject to the following two conditions:

(1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Le présent appareil est conforme aux CNR d'Industrie Canada applicables aux appareils radio exempts de licence. L'exploitation est autorisée aux deux conditions suivantes:

- (1) l'appareil ne doit pas produire de brouillage;

- (2) l'utilisateur de l'appareil doit accepter tout brouillage radioélectrique subi, même si le brouillage est susceptible d'en compromettre le fonctionnement.

#### **8.3.3 RF Exposure Statement:**

This module is approved for installation into mobile and/or portable host platforms.

This device is intended only for OEM integrators under the following conditions:

(1) The transmitter module may not be co-located with any other transmitter or antenna.

(If the condition above is met, further transmitter test will not be required.)

(2) The OEM integrator is still responsible for testing their end-product for any additional compliance requirements required for satisfying RF Exposure compliance when this module installed.

### 8.4 European Union (CE)

#### **8.4.1 Labeling requirements**

The label on the final products which contain the MN54L series module must follow CE marking requirements, should be labelled as follows:

CE logo:

The OEM should consult with a qualified test Lab before entering their device into an EU member country to make sure all regulatory requirements have been met for their complete device.

#### 8.4.2 Radio Equipment Directive (RED)

The MN54L series module complies with the essential requirements and other relevant provisions of Radio Equipment Directive (RED) 2019/07

### 8.5 Australia / New Zealand (RCM)

The MN54L series has been tested to comply with the AS/NZS 62368.1:2022

RCM logo:

### 8.6 NCC Certificate (Taiwan)

#### 8.6.1 NCC ID and Labeling requirements

MN54L 系列依天線不同,可分為 3 種型式,認證為 3 個不同的 NCC ID

MN54L-C NCC ID number:

MN54L-P NCC ID number:

MN54L-U NCC ID number:

請依下列標籤式樣自製標籤,標貼或印鑄於器材(產品)本體明顯處,始得販賣或公開陳列。

**NCC logo and NCC ID**

MN54L-C:

MN54L-P:

#### MN54L-U:

NCC 平台政策下的完全模組: 須符合平台政策才能適用完全模組

「平台」定義如下:若器材無安裝型式認證之模組仍具備其它複合性功能,該 器材得視為平台,若無其它複合性功能,則不能視為平台。

#### NCC 警語:

「取得審驗證明之低功率射頻器材,非經核准,公司、商號或使用者均不得擅自變更頻率、加大功率或變更原設計之特性及功能。低功率射頻器材之使用不得影響飛航安全及干擾合法通信;經發現有干擾現象時,應立即停用,並改善至無干擾時方得繼續使用。前述合法通信,指依電信管理法規定作業之無線電通信。低功率射頻器材須忍受合法通信或工業、科學及醫療用電波輻射性電機設備之干擾。」

## 9. RoHS & REACH Report

MN54L series modules comply with EU RoHS Directive 2011/65/EU, 2015/863/EU and do not contain or over the threshold value of SVHC (Substance of Very High Concern), as defined by Directive EC/1907/2006 Article according to REACH Annex XVII.

## 10. Life support warning

This module is not designed for use in life support appliances, devices, or systems where malfunction can reasonably be expected to result in a significant personal injury to the user, or as a critical component in any life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety.

## **Revision history**

| Version | Date       | Notes           | Name |

|---------|------------|-----------------|------|

| 0.8     | 2025/05/01 | Initial Release |      |

|         |            |                 |      |

|         |            |                 |      |